# Altera Quartus II Tutorial

**CSE140L – WI06**

TA: Jianhua Liu

CSE Dept. UCSD

### Altera Quartus II

- The Quartus II development software provides a complete design environment for FPGA designs.

- Design entry using schematics, block diagrams, VHDL, and Verilog HDL.

- Design analysis and synthesis, fitting, assembling, timing analysis, simulation.

### Altera Quartus II

#### Design flow Quartus II Design entry HDL editor केट Verilog1.v Block diagram, Analysis and radder4.bdf schematic editor synthesis Compiler Tool Compiler tool Fitting Compilation report Compilation Report - Timin... Timing closure Assembling Timing Closure Floorplan floorplan Timing analysis Simulator Tool Simulator tool Simulation Waveform editor radder16.vwf

### **Tutorial Outline**

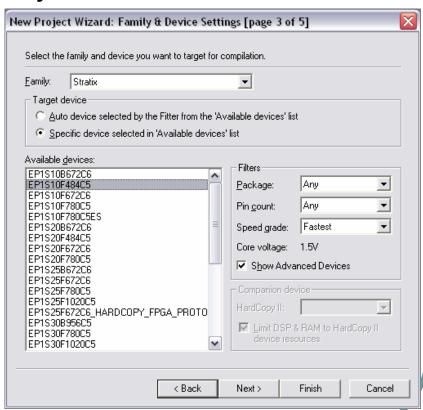

- Open Quartus II and pick a device.

- Build a full adder. (Block/Schematic)

- Add components

- Add ports

- Add connections (single wire connection)

- Build a 4-bit adder.

- Create a block for full adder

- Use conduit and port mapping

#### **Tutorial Outline**

- Compile the 4-bit adder.

- Open compiler tool

- Read compilation report

- Open timing closure floorplan

- Simulate the 4-bit adder.

- Open simulator tool

- Edit simulation waveform

- Observe simulation results

- Schematic for 16-bit Multiplexer

- Use connections by name

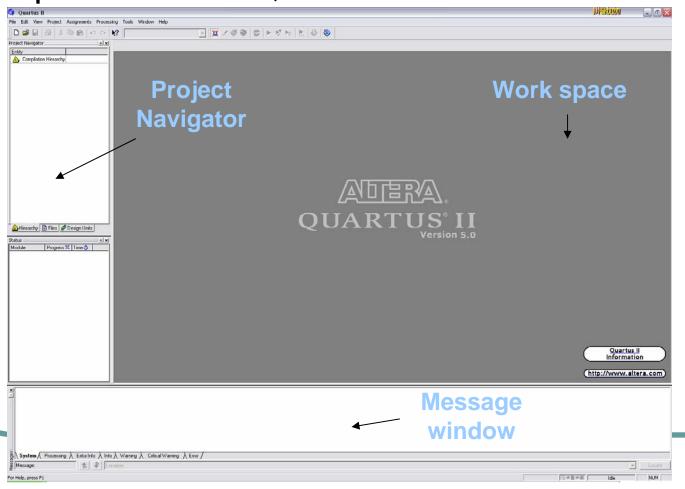

### Start Quartus II

Open Quartus II, click on the icon

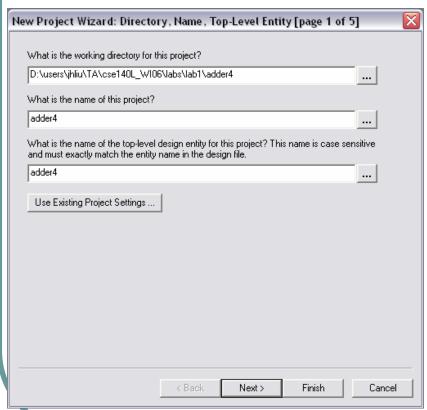

# Create a new project

Menu → File → New Project Wizard

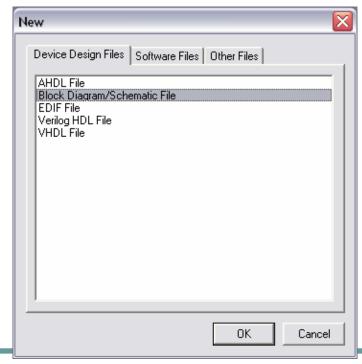

- Menu → File → New

- Create a Block Diagram/Schematic File

- Menu → File → Save As: fadder.bdf

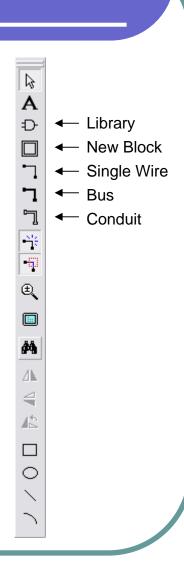

- Click on library

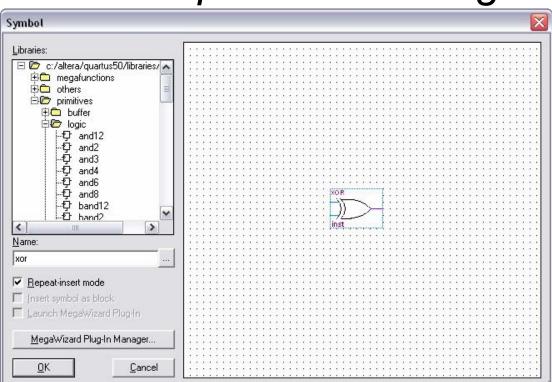

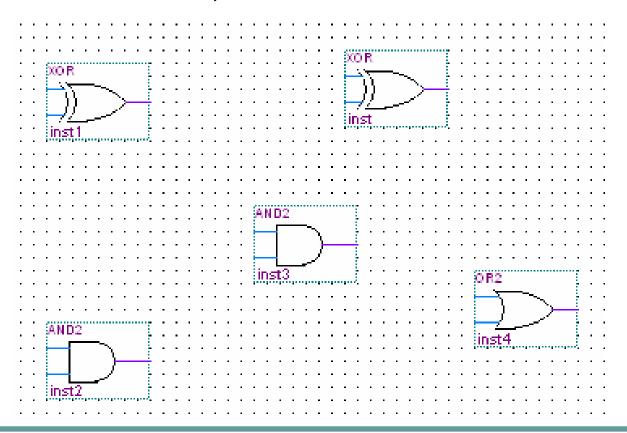

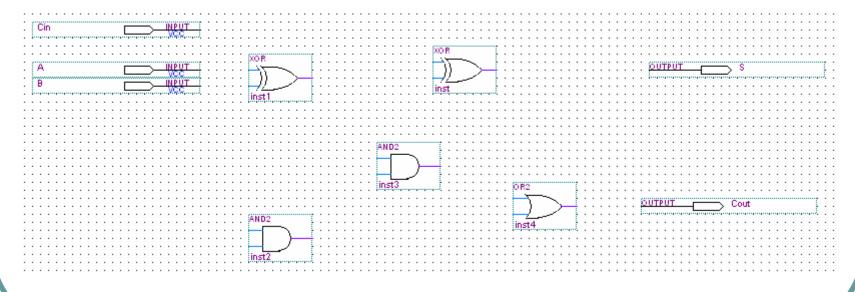

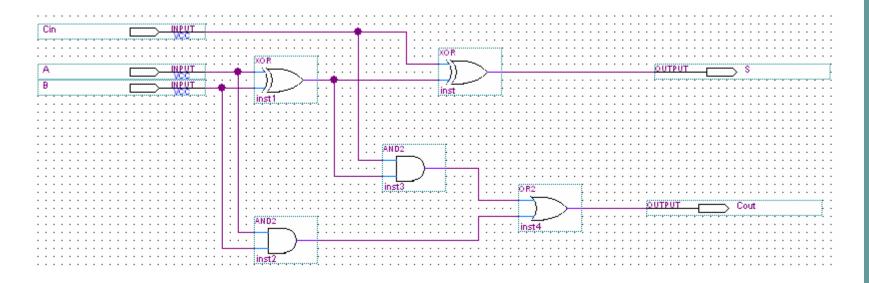

- Find xor under primitives → logic

Place two xor, two and2 and one or2.

- Find input and output under primitives → pin, and place three input and two output

- Double click on each pin, to change pin name.

Connect them by single wire

Save the file

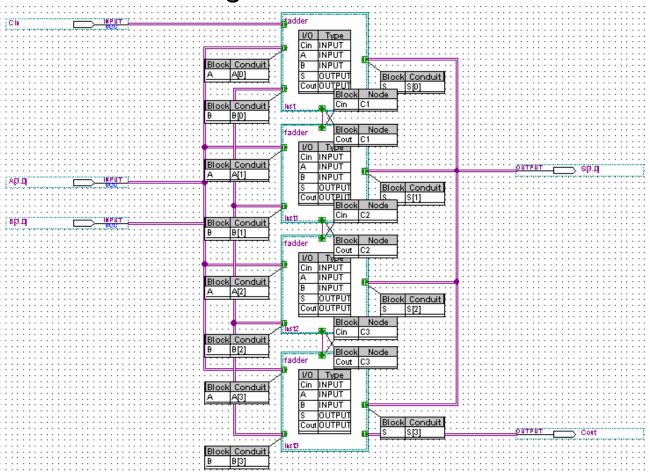

- Menu → File → New

- Create a Block Diagram/Schematic File

- Menu → File → Save As: adder4.bdf

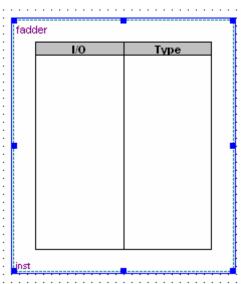

- Click on new block

and draw a block.

- Double click on the block name, change it to fadder

- Right click on the block, and select Block Properties in the pop-up menu.

- In the tag I/Os, add the following ports:

- Click on OK to dismiss the properties window.

- Right click on the block, and select AutoFit in the pop-up menu.

Type

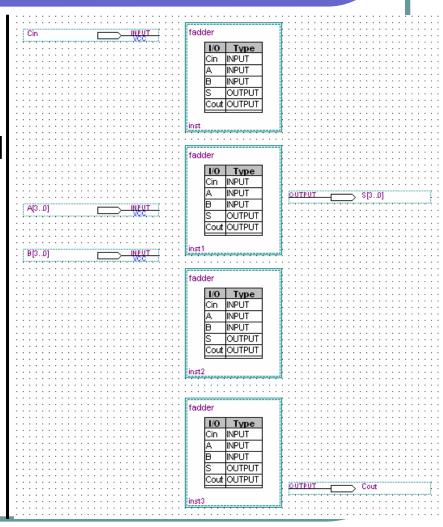

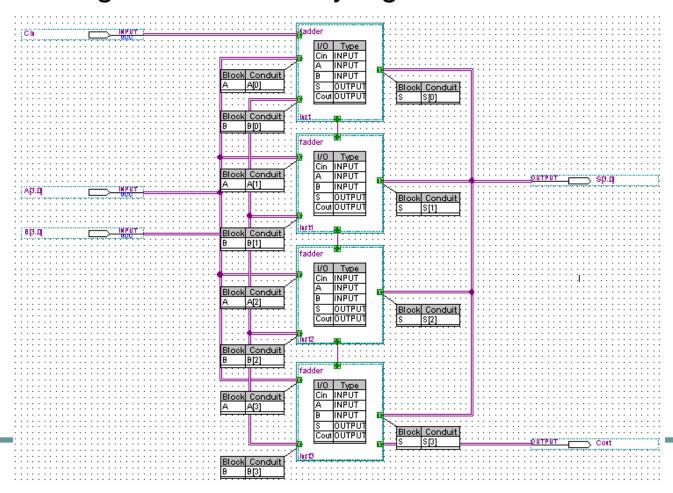

- Select the block, make four copies by copy/paste.

- Add 3 inputs and 2 outputs.

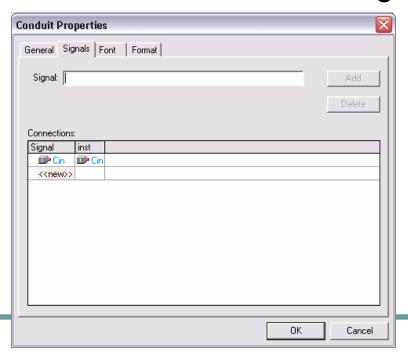

Use conduit tool to connect each fadder to inputs and outputs. Conduit can stop at any point on a block border.

- The primary input *Cin* is automatically connected to the *Cin* port of *inst* by the same same.

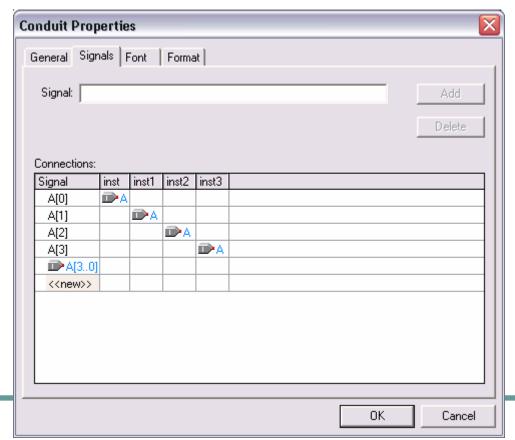

- Right click on the conduit, select *properties*, the connection can be found in the tab *Signals*.

• For A[3..0], B[3..0] and S[3..0], port mapping should be manually defined. Edit the *signals* property for A[3..0]

like this:

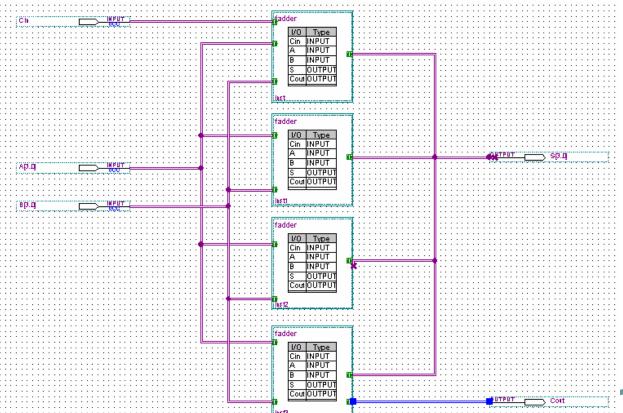

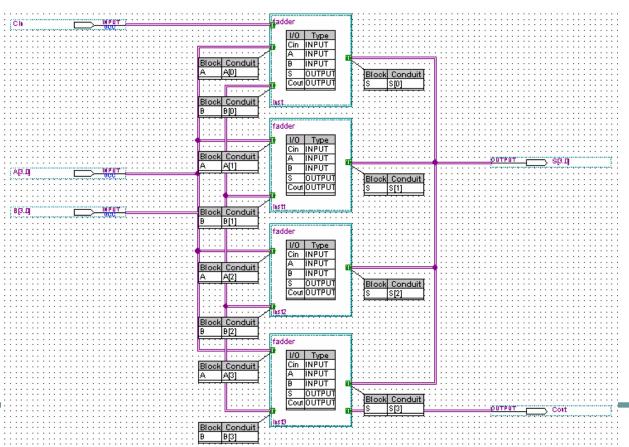

After port mapping for A[3..0], B[3..0] and S[3..0], you will see this:

Place single wires for carry signals.

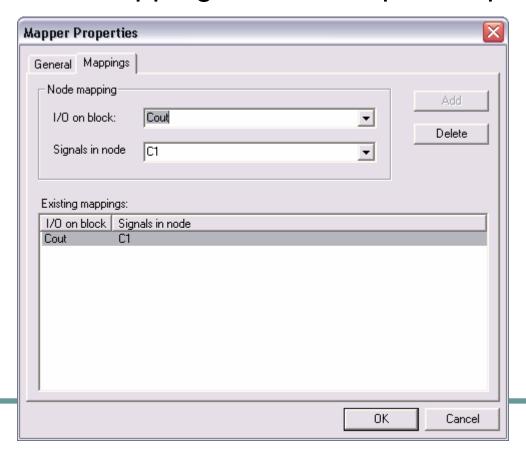

Double click on a port mapper , and define port mapping in the tab Mappings. For example, map Cout

to signal C1.

Here's the final diagram.

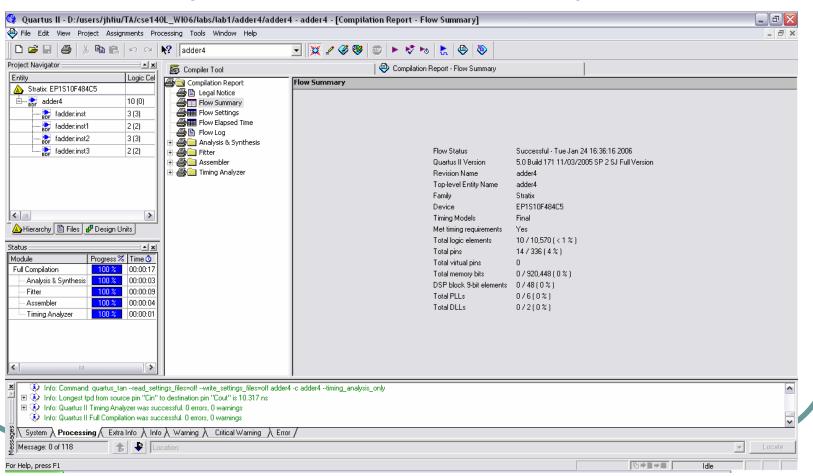

Menu → Tools → Compiler Tool

Click on Start. The design will be compiled automatically.

Click on Report button Properties after compilation.

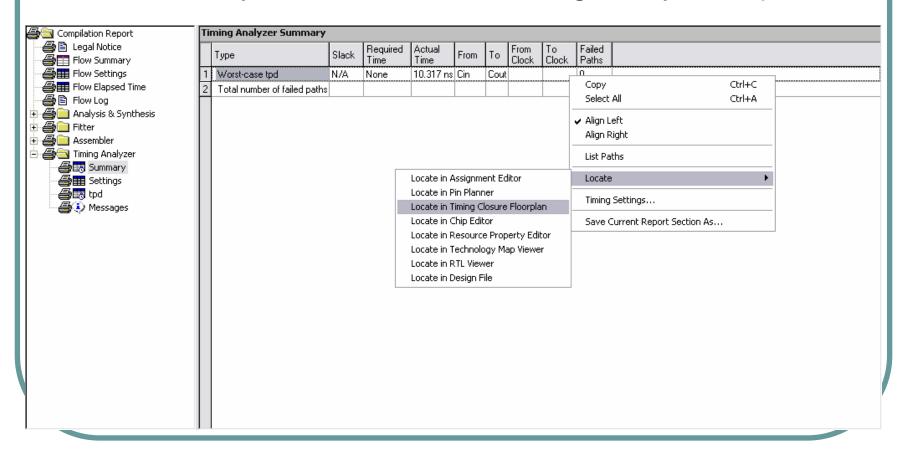

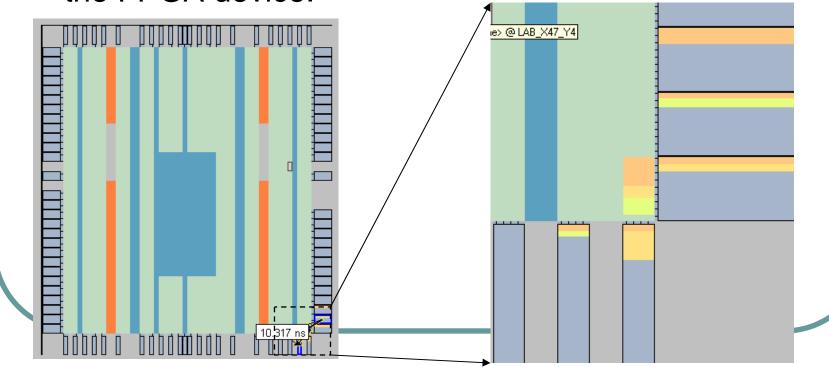

Worst delay can be found in Timing Analyzer report

Select the worst delay, right click on it, and select

*locate* in the pop-up menu → Locate in Timing Closure

Floorplan. You can see the design implementation in

the FPGA device.

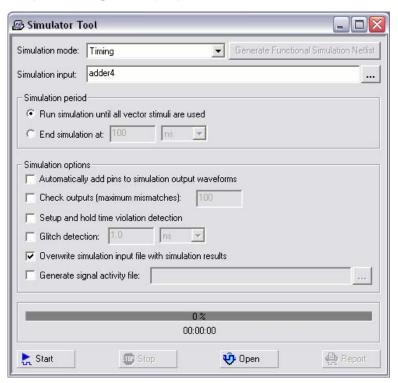

Menu → Tools → Simulator Tool

Type adder4 for Simulation input

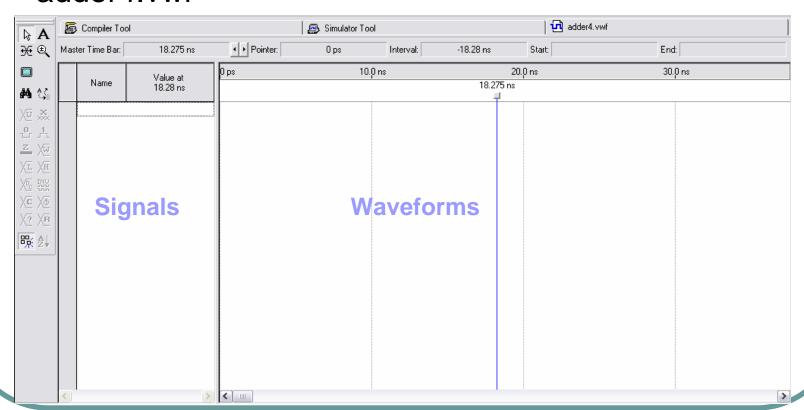

Click on Open button on adder4.vwf

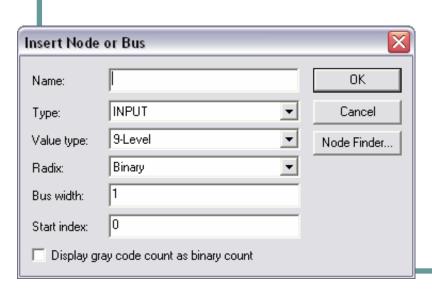

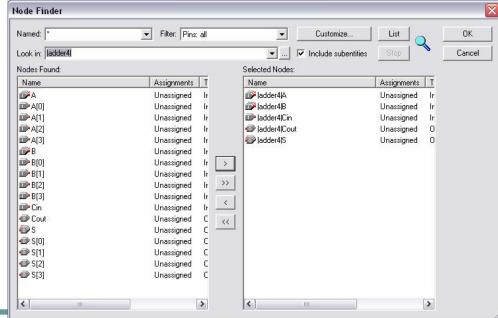

- Double click on signals area, and click the button Node Finder

- List all the pins and select the primary inputs and outputs, then click OK.

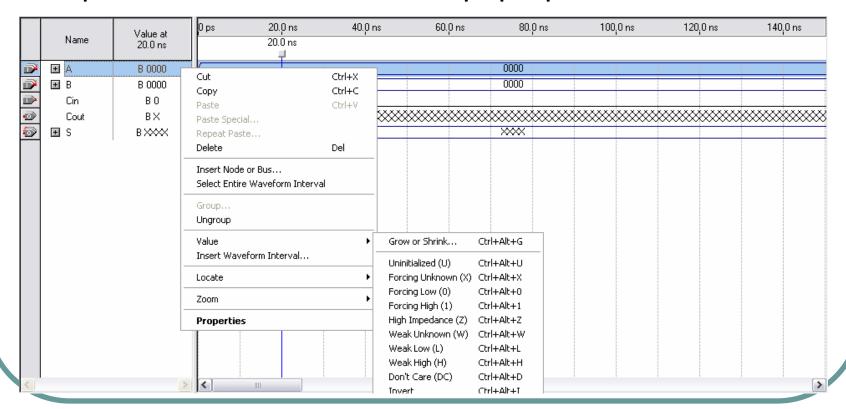

To change the value of each input, right click on the input and select value in the pop-up menu.

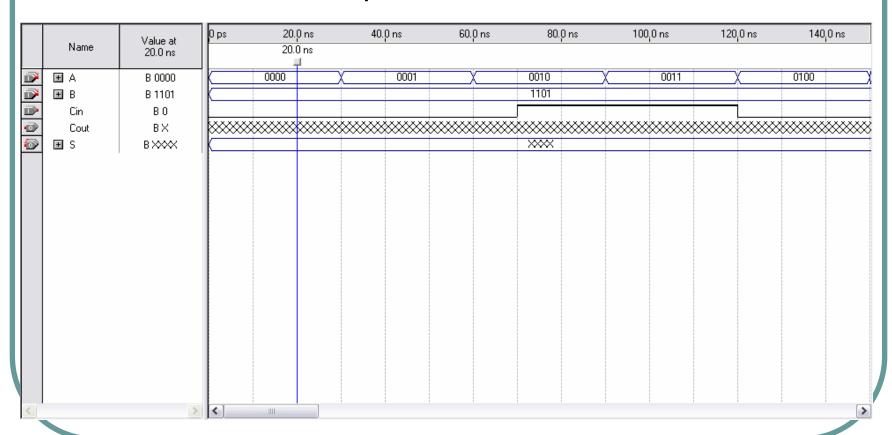

Set value to each inputs and save the file.

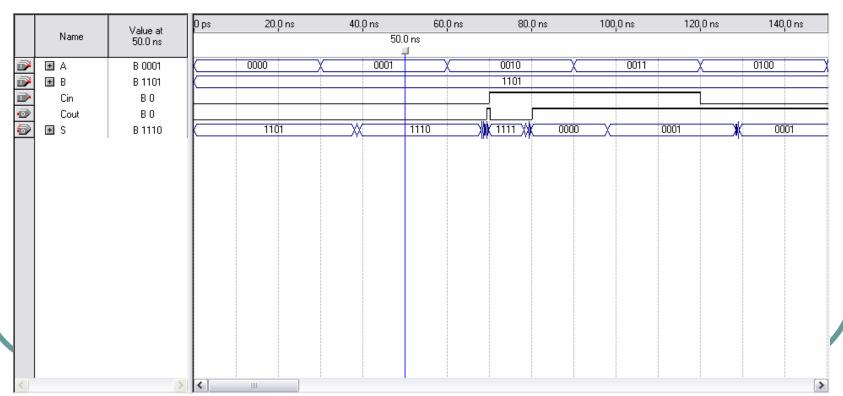

• Go back to the simulator tool, and click on the button Start . adder4.vwf will be updated after the simulation.

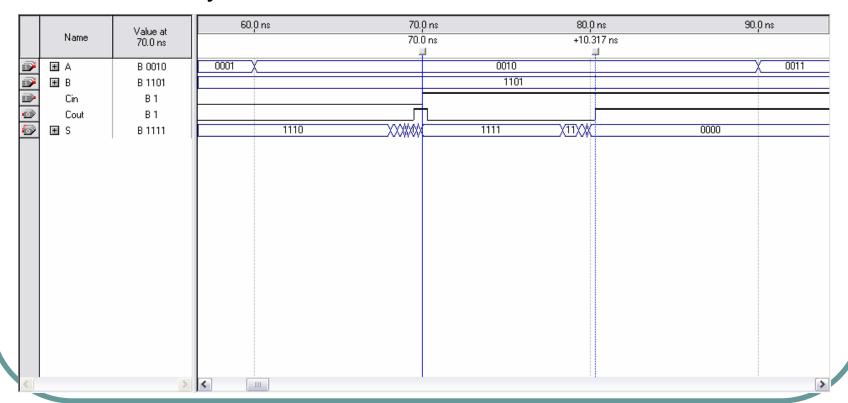

The correctness of the design is verified, and the worst delay can be identified.

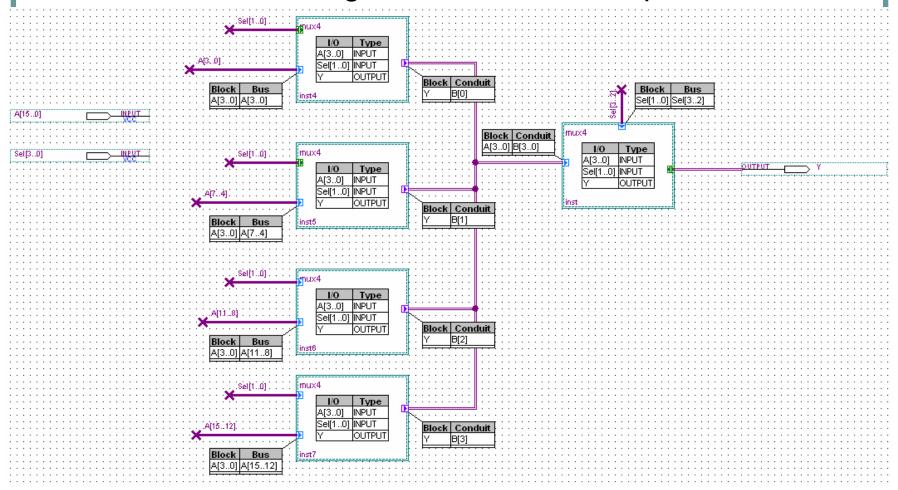

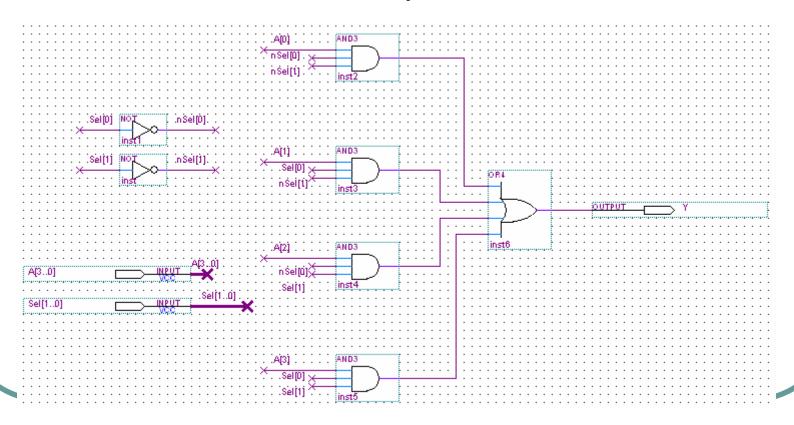

# Schematic for 16-bit Multiplexer

• The schematic diagram of a 4-bit Multiplexer. Note that the wires connected by name.

### Schematic for 16-bit Multiplexer

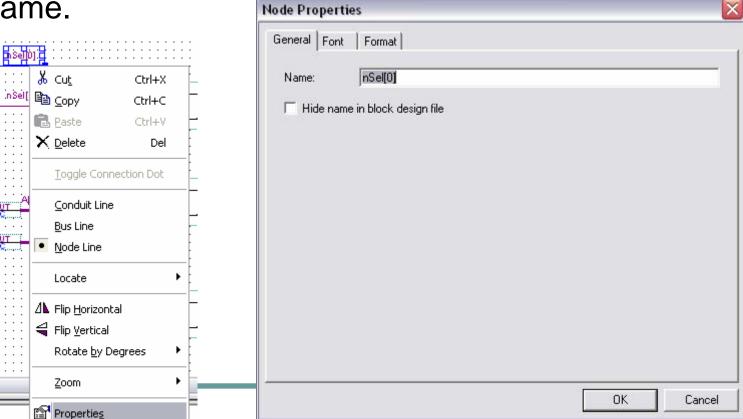

To name a wire/bus, right click the wire/bus, select properties in the pop-up menu, and then fill in the

name.

### Schematic for 16-bit Multiplexer

The schematic diagram of a 16-bit Multiplexer.